# SEK 40C18 Data Sheet

This document provides information on IntellaSys products. No license, expressed or implied, by estoppel or otherwise, to any intellectual property is granted by this document. Except as provided in IntellaSys's Terms and Conditions of Sale for such products, IntellaSys assumes no liability whatsoever.

Copyright (©) Technology Properties Limited (TPL) 2008.

IntellaSys is a TPL Group Enterprise. Printed in the United States of America. All Rights Reserved.

### **Trademarks**

The following items are trademarks or registered trademarks of Technology Properties Limited (TPL): IntellaSys, IntellaSys logo, inventive to the core, SEAforth, Scalable Embedded Array, VentureForth, and Forthlets. All other trademarks and registered trademarks are the property of their respective owners.

### Disclaimer

IntellaSys disclaims any express or implied warranty, relating to sale and/or use of IntellaSys products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

IntellaSys may make changes to specifications and product descriptions contained in this document at any time without notice. Contact your local IntellaSys Sales Office to obtain the latest specifications before placing your purchase order.

### **Patents**

This product includes technology covered by one or more of the following patents and may in addition have U.S. or non U.S. patents pending. U.S. Patents: US 5,440,749; US 5,530,890; US 5,659,703; US 5,784,584. Non U.S. Patents:

DE 0,786,730; EP 0,786,730; FR 0,786,730; IT 0,786,730; NL 0,786,730; GB 0,786,730; JP 2,966,085; EP 0,870,226; IE 0,870,226; GB 0,870,226.

### Revision

| Revision | Date      | Comments |

|----------|-----------|----------|

| 1.1      | 1-10-2009 |          |

|          |           |          |

|          |           |          |

This document contains information proprietary to IntellaSys. Any reproduction, disclosure, or unauthorized use of this document, either in whole or in part, is expressly forbidden without prior permission in writing from:

IntellaSys 20400 Stevens Creek Blvd, Fifth Floor Cupertino CA 95014 USA 408.850.3270 voice 408.850.3280 fax www.intellasys.net

# **Table of Contents**

| 1. | Introduction                                                | 1  |

|----|-------------------------------------------------------------|----|

| 2. | Basic Architecture                                          | 2  |

|    | Figure 1 – S4C180 Evaluation Board Block Diagram            | 2  |

| 3. | Overview                                                    | 3  |

|    | Figure 2 - S40C18 Evaluation Kit                            | 3  |

| 4. | USB Plug-in Board (Dongle)                                  | 4  |

|    | Figure 3 - USB Plug-in Board                                | 4  |

| а  | ı. Software Interface                                       | 4  |

| b  | b. Flash Drive Functionality                                | 4  |

| C  | c. Activity LED                                             | 5  |

| d  | d. S40C18 Connector                                         | 5  |

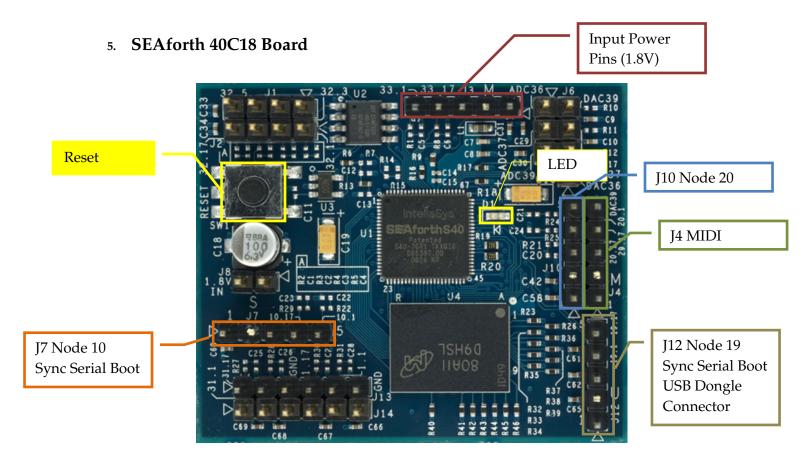

| 5. | SEAforth 40C18 Board                                        | 6  |

|    | Figure 4 – SEAforth 40C18 Board                             | 6  |

| а  | a. Reset Circuit                                            | 6  |

| C  | SPI Boot Control                                            | 6  |

| d  | d. LED                                                      | 7  |

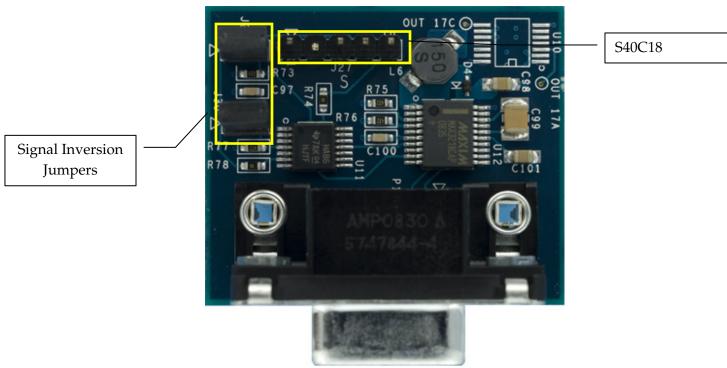

| 6. | RS232 Dongle                                                | 8  |

|    | Figure 5 - RS232 Dongle                                     | 8  |

| 7. | Prototyping Area and Level Shifter Board                    | 9  |

|    | Figure 7 – Midi Input and Audio Board                       | 10 |

| Ap | pendix A – SEAforth 40C18 Signals and Corresponding Headers | 12 |

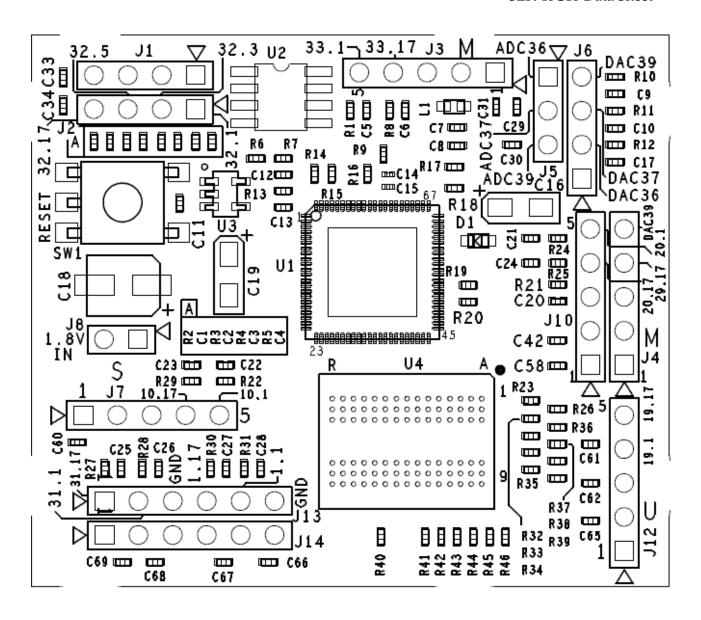

|    | Figure 8 – SEK 40C18 Board Layout                           | 13 |

| Ap | ppendix B – Board Errata                                    | 15 |

# 1. Introduction

The purpose of the SEAforth 40C18 Evaluation Board is meant for the evaluation of the S40C18 chip. The purpose of the board is to facilitate the prototyping of applications and application code. This document covers the evaluation board only. For more information on the SEAforth 40C18 chip itself, please refer to the datasheet. This reference manual is not meant as a user guide, but to be used as a reference to specific functions of the board as needed.

# 2. Basic Architecture

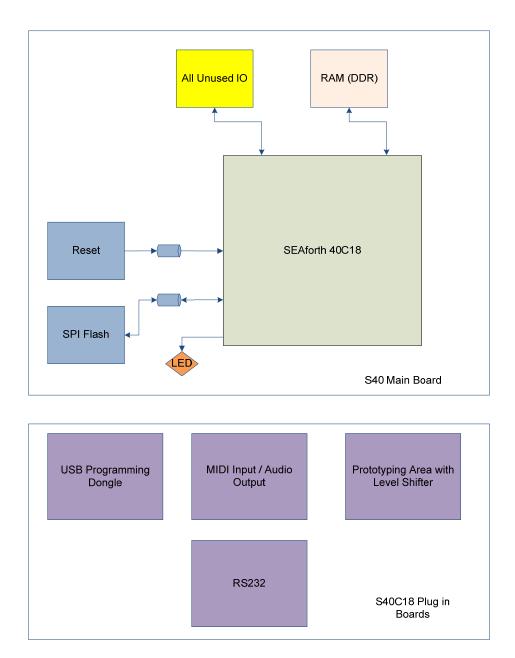

The basic functional blocks of the Evaluation Board are illustrated below in Figure 1.

Figure 1 – S40C18 Evaluation Board Block Diagram

# 3. Overview

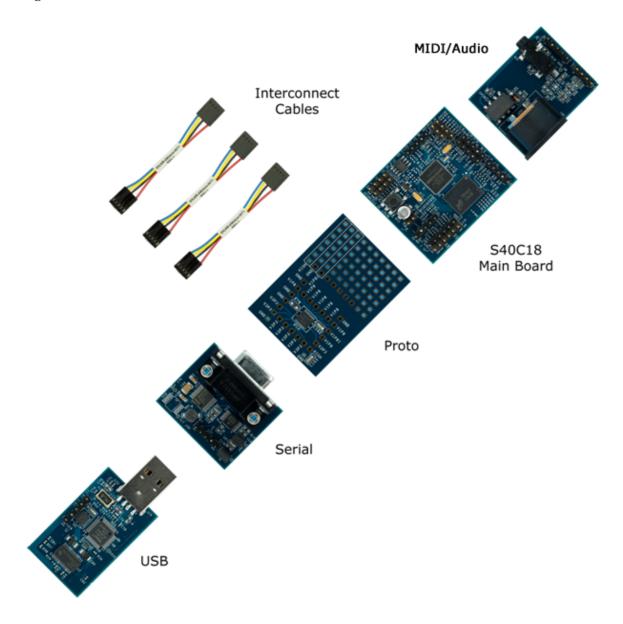

The physical PCB is pictured below in Figure 2. The basic areas are marked in this figure, and more detail will be discussed in later sections.

Figure 2 - S40C18 Evaluation Kit

# 4. USB Plug-in Board (Dongle)

The USB interface is the same as the FORTHdrive<sup>™</sup>. The board supplies communications between the S40C18 and the PC via node 19 on the chip and alternatively node 10. The PC end is controlled using the VentureForth® software included with the kit.

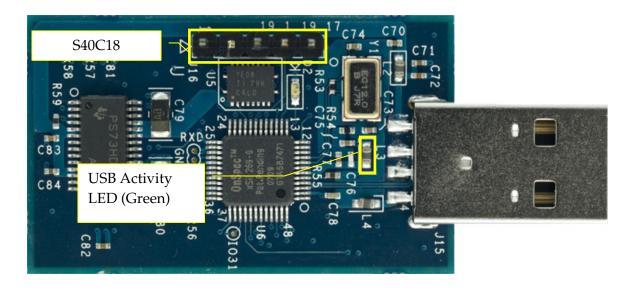

Figure 3 - USB Plug-in Board

# a. Software Interface

The USB interface is identical to that of the 24 node FORTHdrive. The software interface is also identical. Please reference the software manual for more information.

# b. Flash Drive Functionality

The USB interface also gives the test board the facility to operate as a typical 1GB capacity USB Mass Storage Device (Flash Drive). A new drive letter with the name "SEAforth" will appear on windows systems when connected via USB.

# c. Activity LED

The green activity LED is normally on, indicating that the USB dongle has power and is connected to a USB master. The LED blinks when the NAND flash is being accessed.

### d. S40C18 Connector

The USB board has a five pin connector that is used to connect to the S40C18 board J12. It can also be connected to J7 to allow booting from node 10. The signals are to be connected to the corresponding signals on the SEAforth 40C18 board. The pins are as follows:

| Pin Number | Signal Name    |

|------------|----------------|

| 1          | 1.8V Out       |

| 2          | NC             |

| 3          | GND            |

| 4          | SIO19.17 Clock |

| 5          | S1019.1 Data   |

Figure 4 - SEAforth 40C18 Board

### a. Reset Circuit

The reset on board is handled by a reset chip with a manual input switch. The default delay for reset is released 20µs after 1.8V I/O is stable.

### b. Power Using the USB Dongle

The USB dongle can also be used to supply power to the board, but only in low load situations. The purpose of the power from the USB dongle is to facilitate quick loading of new code without having to manually power cycle the board. If it is desired to always use a separate 1.8v power source, please use the USB dongle cable without the power wires (Gnd and pin 3).

### c. SPI Boot Control

If the flash has not been programmed, node 32 will see this as invalid and not attempting to boot from the flash. If the flash has been programmed, after rest node 32 will always attempt to boot from the flash unless S1032\_17\_sf is pulled high. This can be accomplished by placing a jumper with a resistance of 3.3k

between J2-4 and J1-3. This will allow you to regain control of node 32 so the program in the flash can be changed or allow other nodes to be booted from without interference from, the program saved in the serial flash.

### d. LED

There is an amber LED connected to the S40C18 on Node29 bit 1. This can be used at the programmer's discretion. The LED is synced by the SEAforth. This means a low voltage on the pin illuminates the LED, and a high voltage deactivates the LED.

### e. I/O Pins

All IO Pins are clearly marked on the silkscreen of the board. Please see appendix for list of signals and associated connectors

# 6. RS232 Dongle

A RS-232 dongle has also been included in the kit as a serial communications option.

Figure 5 - RS232 Dongle

### Connection to SEAforth S40C18 Board

a. The RS232 board connects to the SEAforth 40C18 board via a 5 pin connector. The pinout is as follows:

| Pin Number | Signal Name                      |

|------------|----------------------------------|

| 1          | 1.8V in                          |

| 2          | NC                               |

| 3          | GND                              |

| 4          | Receive (from PC point of view)  |

| 5          | Transmit (from PC point of view) |

This can be connected to J7 on the main board, which is the connector currently most often for serial I/O. This directs the serial I/O through node 10. This can also be connected to the J3, J10, or J12. If you are using J12 for serial I/O, the SEAforth will need to boot from either node 10, 32 or 33.

# b. Signal Inversion

Jumpers J26 (receive) and J30 (transmit) supply optional inversion of the signals depending on the orientation of the host system. By default, the jumpers are closed.

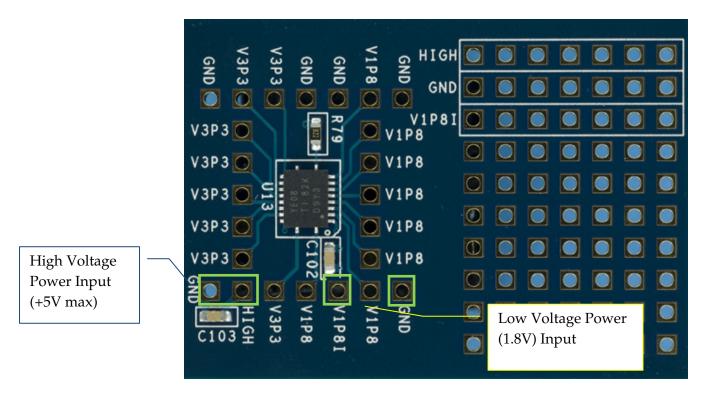

# 7. Prototyping Area and Level Shifter Board

The prototyping area provides an area for extra components for customer use. The on-board bi-directional level shifter provides the shifting of signals from high as 5V down to the S40C18's native 1.8V signal levels and visa versa.

Figure 6 - Prototyping Board

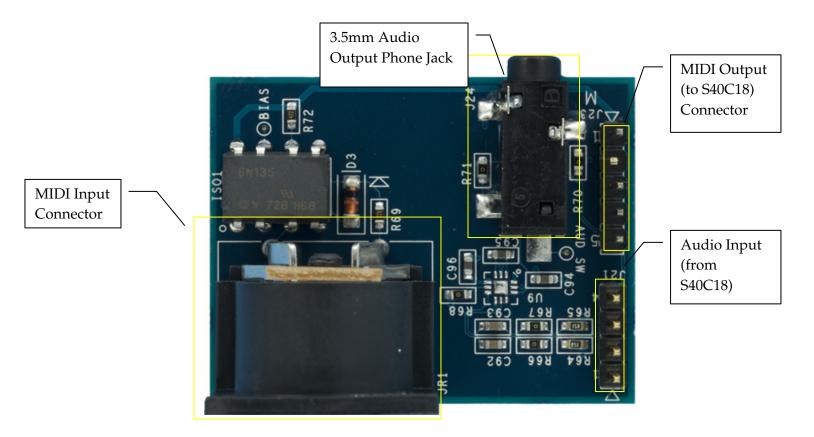

# 8. MIDI Input and Audio Board

The midi board has the  $75\Omega$  load resistors required for the DAC already installed on board. The default wiring scheme has the S40C18 directly driving the user supplied speaker or amplifier plugged into the 3.5 mm audio jack. A footprint is supplied for the installation of an optional headphone driver IC.

Figure 7 - Midi Input and Audio Board

Midi output (to S40C18) Connector

| Pin Number | Signal Name |

|------------|-------------|

| 1          | 1.8V In     |

| 2          | NC          |

| 3          | GND         |

| 4          | MIDI        |

| 5          | RIGHT       |

# Audio Input (to S40C18) Connector

| Pin Number | Signal Name                        |  |  |  |  |

|------------|------------------------------------|--|--|--|--|

| 1          | BV In (Optional for Headphone Amp) |  |  |  |  |

| 2          | LEFT                               |  |  |  |  |

| 3          | RIGHT                              |  |  |  |  |

| 4          | AGND                               |  |  |  |  |

Note: A jumper can be placed across Pin 2 and Pin 3 to connect both the left and right out to DAC39.

# Appendix A – SEAforth 40C18 Signals and Corresponding Headers

| Category | SEAforth 40C18 Signal | Header/Connector |  |  |  |

|----------|-----------------------|------------------|--|--|--|

|          |                       |                  |  |  |  |

| ADC36    | ADC36_sf              | J5-1             |  |  |  |

| ADC37    | ADC37_sf              | J5-2             |  |  |  |

| ADC39    | ADC39_sf              | J5-3             |  |  |  |

|          |                       |                  |  |  |  |

| DAC36    | DAC36_sf              | J6-2             |  |  |  |

| DAC37    | DAC37_sf              | J6-3             |  |  |  |

| DAC39    | DAC39_sf              | J6-4             |  |  |  |

|          |                       |                  |  |  |  |

| 1_1      | S101_1_sf             | J13-5            |  |  |  |

| 1_17     | S101_17_sf            | J13-4            |  |  |  |

| 10_1     | S1010_1_sf            | J7-5             |  |  |  |

| 10_17    | S1010_17_sf           | J7-4             |  |  |  |

| 19_1     | S1019_1_sf            | J12-5            |  |  |  |

| 19_17    | S1019_17_sf           | J12-4            |  |  |  |

| 20_1     | S1020_1_sf            | J10-5            |  |  |  |

| 20_17    | S1020_17_sf           | J10-4            |  |  |  |

| 29_1     | S1029_1_sf            | LED              |  |  |  |

| 29_17    | S1029_17_sf           | J4-4             |  |  |  |

| 31_1     | S1031_1_sf            | J13-2            |  |  |  |

| 31_17    | S1031_17_sf           | J13-1            |  |  |  |

| 32_1     | S1032_1_sf (SPI_en)   | J2-1             |  |  |  |

| 32_3     | S1032_3_sf (SPI_en)   | J2-2             |  |  |  |

| 32_5     | S1032_5_sf (SPI_do)   | J2-3             |  |  |  |

| 32_17    | S1032_17_sf (SPI_di)  | J2-4             |  |  |  |

| 33_1     | S1033_1_sf            | J3-5             |  |  |  |

| 33_17    | S1033_17_sf           | J3-4             |  |  |  |

| 38_17    | S1038_17_sf           | J6-1             |  |  |  |

Note: For the DAC outputs to be properly observed, they will need to be connected to a 75 OHM resistor to ground. This load resistor is included on the MIDI board. When not using the MIDI module, an external resistor needs to be used for each DAC used.

Figure 8 - SEK 40C18 Board Layout

# **Connector Pinouts**

|     |          | _ |     |          |   |     |        | _ |     |          |

|-----|----------|---|-----|----------|---|-----|--------|---|-----|----------|

|     | J7       |   |     | J6       |   |     | J5     |   |     | J8       |

| PIN | Signal   | F | PIN | Signal   |   | PIN | Signal |   | PIN | Signal   |

| 1   | V1P8     |   | 1   | SIO38_17 |   | 1   | ADC36  |   | 1   | V1P8     |

| 2   | NC       |   | 2   | DAC36    |   | 2   | ADC37  |   | 2   | GND      |

| 3   | GND      |   | 3   | DAC37    |   | 3   | ADC39  |   |     |          |

| 4   | SIO10_17 |   | 4   | DAC39    |   |     |        | _ |     | J13      |

| 5   | SIO10_1  | _ | _   | _        |   |     | J14    |   | PIN | Signal   |

|     |          |   |     |          |   | PIN | Signal |   | 1   | SIO31_17 |

|     | J3       |   |     | J10      |   | 1   | GND    |   | 2   | SIO31_1  |

| PIN | Signal   | F | PIN | Signal   |   | 2   | V1P8   |   | 3   | GND      |

| 1   | V1P8     |   | 1   | V1P8     |   | 3   | GND    |   | 4   | SIO1_17  |

| 2   | NC       |   | 2   | NC       |   | 4   | GND    |   | 5   | SIO1_1   |

| 3   | GND      |   | 3   | GND      |   | 5   | V1P8   |   | 6   | GND      |

| 4   | SIO33_17 |   | 4   | SIO20_17 |   | 6   | V1P8   |   |     |          |

| 5   | SIO33_1  |   | 5   | SIO20_1  |   |     |        |   |     |          |

|     |          |   |     |          | - |     |        |   |     |          |

|     | J4       |   |     | J12      |   |     | J1     |   |     | J2       |

| PIN | Signal   | F | PIN | Signal   |   | PIN | Signal |   | PIN | Signal   |

| 1   | V1P8     |   | 1   | V1P8     |   | 1   | V1P8   |   | 1   | SIO32_1  |

| 2   | NC       |   | 2   | NC       |   | 2   | GND    |   | 2   | SIO32_3  |

| 3   | GND      |   | 3   | GND      |   | 3   | V1P8   |   | 3   | SIO32_5  |

| 4   | SIO29_17 |   | 4   | SIO19_17 |   | 4   | GND    |   | 4   | SIO32_17 |

| 5   | SIO29_1  | L | 5   | SIO19_1  |   |     |        |   |     |          |

# Appendix B – Board Errata

Board Version 0.01 – Last Updated 03/05/2008